DSP應用實驗說明與分析

2026-01-15 08:53DSP應用實驗(yàn)說明與分析實驗目的

1.熟悉DSP定時器/計數(shù)器、I/O口使用、DSP緩衝串口的使用、各存貯空間訪問等基本原理;

2.熟悉DSP的指令係統。

二、實驗原理說明(míng)

實驗平台提供DSP應用的硬(yìng)件(jiàn)支持有:基本I/O口XF的使用(有發光(guāng)二極管[XF]指示(shì)和(hé)測試點(diǎn)[TPXF])、定時器/計數器使用(定時溢(yì)出,有發光二極管指示[TOUT]和測試點(diǎn)[TPTOUT])、串行方式的A/D接口、串行方式的D/A接口。

選擇哪部分的應用(yòng)實驗(yàn)就應查閱相應(yīng)的DSP資料,如定時器使(shǐ)用部分:

C5402的定(dìng)時器/計數器有2個,工業應用中,計數器和定時器常用(yòng)於檢測及控製。這些定時器可能通過(guò)軟件編程或硬件鎖相(xiàng)環精確(què)定時。該(gāi)實驗以方波發生器(qì)為例介紹定時器的編(biān)程,時鍾頻率為16.384MHz,在XF端輸出一個周期為20ms的方波,方波的周期由片(piàn)上定時器確定,采(cǎi)用中斷方法實現。

1.定時器0的初始化:

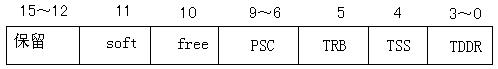

1)設置定時控製寄存器TCR(地址0024H)

15~12(保留位):通常(cháng)情(qíng)況下設置為(wéi)0000

11(soft)和10(free)軟件(jiàn)調(diào)試控製位:

free=0、soft=0時定時器立(lì)即停止工(gōng)作。

free=0、soft=1且計數器TIM減為1時,定時器停(tíng)止工作。

ree=1、soft=X時,定時器繼續工作。該例中設free=1、soft=0。

9~6(PSC)預定標計數器:複位或其減為0時(shí),分頻係數(shù)TDDR自動加載到PSC上。該例中設置TDDR=1001H=9。

5(TRB)定時器重新加載控製位:用於複位片內定時器。當TRB=1,預標定分頻係數TDDR和定時器周(zhōu)期寄存器PRD中的數據(jù)分別加載到定時器預標定計數器PSC和定時器TIM中。該例中設TRB=1。

4(TSS)定時器停止控製位:用於停止啟動(dòng)定時器。當(dāng)TSS=0時定時器(qì)啟(qǐ)動開始工作。當TSS=1時,定時器(qì)停(tíng)止工作。該例中設TSS=0。

3~0(TDDR)預標定分(fèn)頻係數:最(zuì)大(dà)的預標定值(zhí)為(wéi)16,最小(xiǎo)值為1。按照這(zhè)個分(fèn)頻係數,定時器對(duì)時鍾輸出信號CLKOUT進(jìn)行分頻,分頻是通過預標定計(jì)數器PSC進行的。當(dāng)複位或減為0時,分頻係數TDDR自動加載到PSC上(shàng),開始新一輪計數。該(gāi)例中設置TDDR=1001H=9。

最後程序中(zhōng)設置TCR=669H

2)設置定時寄存器TIM(地(dì)址0025H);複位時,TIM和PRD為0FFFFH,TIM由PRD中的數據加載。

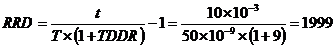

3)設置定時周期寄存器PRD(地址0026H):因為(wéi)輸出脈衝(chōng)周期為20ms,所(suǒ)以定時中(zhōng)斷周期應該為10ms,每(měi)中斷一次,輸出端電(diàn)平(píng)取反一次。

定時(shí)時間計算公式:t=T×(1+TDDR)×(1+PRD)=10ms

T:CLKOUT主頻f=16.384MHz,T=61ns;給定TDDR=9,

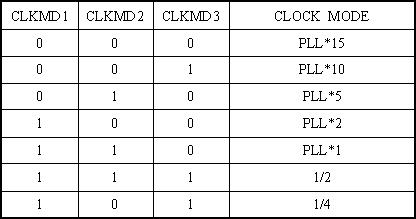

2.定時器是對c5402的主時鍾CLKOUT進行分頻的。CLKOUT與外部晶體振蕩器頻(pín)率(在本實驗係統中外部晶體振蒎器的頻(pín)率為16.384MHz)之間的關係的c5402的三個(gè)引腳CLKMD1、CLKMD2、CLKMD3的電平值決定,具體關係如表18-1所示:

表21-1

在本實驗係統中,使用的主時鍾頻率,為81.925MHz(CLKMD1=0、CLKMD2=1和CLKMD3=0)。

3.中斷初始化

1)中斷屏蔽寄存器(qì)IMR中的定時屏蔽位TINT0置1,開放定(dìng)時器0中(zhōng)斷(duàn)。

2)狀態控(kòng)製寄存器ST1中的中斷標誌位INTM位清零,開放全部中斷。

三、實驗內容(róng)

1.編寫並實現20ms溢出率的定時程序,並使DSP的XF腳每20ms電平變化一次(cì)即使其對應的發光二極管(guǎn)閃爍,用示波器檢測XF(TPXF)上的信號周期(qī)是否正確?

2.認真(zhēn)閱讀TLC5608D/A變換芯片的資料,編寫D/A變換的(de)軟(ruǎn)件,使8路D/A分別輸出鋸齒波(bō)。

3.認(rèn)真閱讀TLC1572A/D變換芯片的資料,編寫A/D變(biàn)換的軟件,使8路D/A分別(bié)輸出采集到(dào)的輸入信號。

四、實驗報告要求

1.總結定時器/計數器、DSP緩衝串口的原理與應用,並(bìng)寫出各(gè)寄存器的控製字;

2.給出相應程序的(de)框圖。

五、實驗設備(bèi)

1.雙蹤示波器1台

2.信號與係統實驗(yàn)箱1台